This is one of the questions most frequently asked by manufacturers. POWERLINK can generally be integrated into any standard embedded Ethernet design either as a pure software solution or with hardware support, regardless of the processor architecture being used. For pure software solutions, POWERLINK is directly integrated on the application processor and uses a standard Ethernet controller as its bus connection. If very demanding requirements call for hardware acceleration, a number of manufacturers give users a broad variety of options permitting them to implement solutions tailored to their needs, none of which require proprietary technology such as ASICs.

100% open technology

POWERLINK is an open technology, which always gives customers the choice among various POWERLINK manufacturers and service providers (see “Technology providers” section) and ensures an optimal price/performance ratio for every application. Regardless of whether time to market or price is the key criteria – this open software solution with a consistent specification provides users with greater freedom and more opportunities for technical optimizations than other comparable real-time Ethernet systems.

openPOWERLINK

openPOWERLINK is a complete protocol solution for masters and slaves. Programmed in ANSI C, this implementation can be easily ported to any target system. openPOWERLINK has been released on the SourceForge code repository under the BSD license, which grants permission for anyone to use, distribute, modify and enhance the software free of charge. It is also possible for developers to integrate the software into retail products and source code for custom modifications without disclosure.

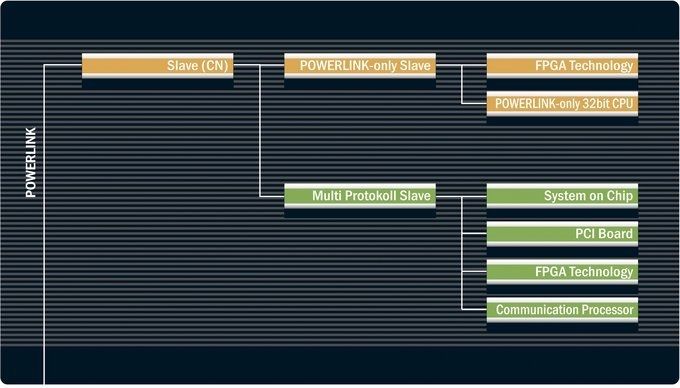

POWERLINK Slave

In addition to the implementation of POWERLINK slaves as stacks on the application processor, slaves can also be based on dedicated communication hardware. POWERLINK slave implementation types range from ready-to-run evaluation boards and piggyback-style single boards, which are suitable for prototyping or for series manufacturing of smaller batches, to optimized FPGA-based chip solutions complete with the protocol as well as the application software. These various options differ in terms of flexibility as well as cost. Multi-protocol solutions allow component manufacturers to use a consistent hardware platform that is open for various industrial Ethernet solutions. A decision for using a specific fieldbus is made when a product is customized to be shipped to an end user. This option is usually more expensive than dedicated "POWERLINK-only" solutions.

Multi-protocol ASICs accommodate the entire system design in one chip. Benefits include the defined interface between the communication processor and application processor, but there are also drawbacks such as the fixed programming interface, more expensive hardware and costs that vary with production batches. Multi-protocol FPGA solutions provide flexibility for environments where different protocols are used. In contrast to ASIC solutions, users can influence the API; however, they should be aware that hardware costs are contingent on the resource requirements of the most demanding protocol involved. "POWERLINK-only" FPGA solutions provide more economic alternatives and additional flexibility with respect to the interface. Conventional 32-bit CPUs equipped with RAM and internal flash memory represent the most cost-efficient option for connecting a slave, clearly undercutting the price range of ASIC-based protocols while still ensuring that users enjoy the flexibility and openness of a standard microprocessor. A characteristic common to all options is the flexible connection of the application and communication software, e.g. via dual-ported RAM or serial interface.

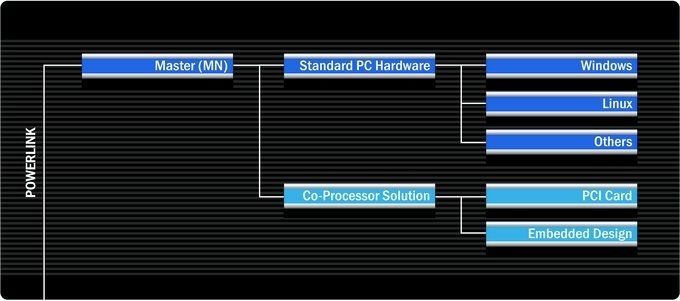

POWERLINK Master

POWERLINK can be used without hardware support on any operating system of choice (e.g. Windows, Linux or VxWorks) with a standard onboard Ethernet controller. Achievable jitter and cycle times are contingent on CPU performance and an optimal adaptation of the operating system to the CPU. Cycle times around 500 µs and jitter values of about 30 µs are typical. Integrating a PCI card with pre-implemented POWERLINK into the system is an alternative option to a POWERLINK master. In this scenario, a co-processor handles the protocol stack and saves central processor resources, typically achieving cycle times of 100 µs and an accuracy of 0.1 µs.